# PRELIMINARY

# **CLASS D AMPLIFIER FOR DIGITAL AUDIO**

### GENERAL DESCRIPTION

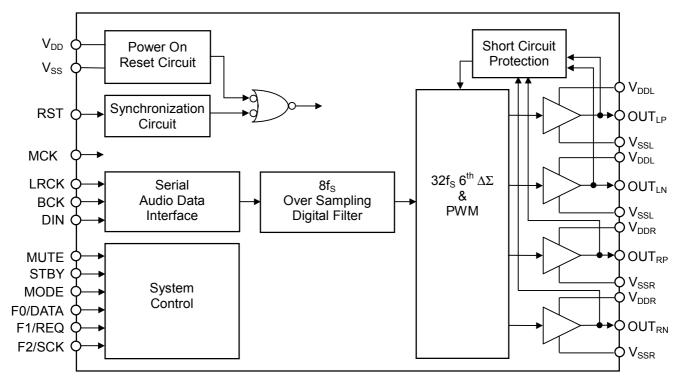

The NJU8725 is an 800mW-output class D Amplifier featuring  $6^{th} \Delta \Sigma$  modulation. It includes Digital Attenuator, Mute, and De-emphasis circuits. It converts Digital source input to PWM signal output which is output PWM signal converted to analog signal with simple external LC Filter. The NJU8725 realizes very high power-efficiency by class D operation. Therefore, it is suitable for battery-powered applications and others.

NJU8725V

### **PIN CONFIGURATION**

FEATURES Stereo BTL Power Amplifier Sixth-order  $32f_S$  Over Sampling  $\Delta\Sigma$  & PWM VDDC 1 24 ⊐ F0/DATA Internal 8fs Over Sampling Digital Filter STBY 2 23 ⊐F1/REQ Sampling Frequency : 96kHz (Max.) TEST 3 22 □F2/SCK De-Emphasis 32kHz, 44,1kHz, 48kHz 4 21 DIN MUTE System Clock : 256fs 5 **Digital Processing** : Attenuator 107step, LOG Curve 20 : Mute 6 OUTLPE 19 Digital Audio Interface : 16bit, 18bit 7 ⊐V<sub>SSR</sub> V<sub>SSL</sub>C 18 : I<sup>2</sup>S, LSB Justified, MSB Justified 8 17 Short Circuit Protection 9 16 V<sub>DDL</sub>C **Operating Voltage** : 3.0 to 3.6V Driving Voltage : V<sub>DD</sub> to 5.25V MODE C 10 15 ⊐LRCK C-MOS Technology RST 11 14 ⊐BCK Package Outline : SSOP24 12 ⊐MCK V<sub>SS</sub>E 13

### **BLOCK DIAGRAM**

# ■ TERMINAL DESCRIPTION

| No.        | SYMBOL            | I/O                                                        | FUNCTION                                                                                                                          |  |  |

|------------|-------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | V <sub>DD</sub>   | -                                                          | Logic Power Supply, V <sub>DD</sub> =3.3V                                                                                         |  |  |

| 2          | STBY              |                                                            | Standby Control Terminal                                                                                                          |  |  |

| 2          | 3101              | I                                                          | Low : Standby ON High : Standby OFF                                                                                               |  |  |

| 3          | TEST              |                                                            | Manufacturer Testing Terminal                                                                                                     |  |  |

| 3          | TLOT              |                                                            | Normally connect to GND.                                                                                                          |  |  |

| 4          | MUTE              |                                                            | Mute Control Terminal                                                                                                             |  |  |

|            |                   | -                                                          | Low : Mute ON High : Mute OFF                                                                                                     |  |  |

| 5          | V <sub>DDL</sub>  | -                                                          | Lch Power Supply, $V_{DDL}=V_{DD}$ to 5.0V                                                                                        |  |  |

| 6          | OUT <sub>LP</sub> | 0                                                          | Lch Positive Output Terminal                                                                                                      |  |  |

| 7          | V <sub>SSL</sub>  | -                                                          | Lch Power GND, V <sub>SSL</sub> =0V                                                                                               |  |  |

| 8          |                   | 0                                                          | Lch Negative Output Terminal                                                                                                      |  |  |

| 9          | V <sub>DDL</sub>  | -                                                          | Lch Power Supply, $V_{DDL}=V_{DD}$ to 5.0V                                                                                        |  |  |

| 10         | MODE              |                                                            | Control Mode selection Terminal                                                                                                   |  |  |

|            |                   | -                                                          | Low : Parallel Control Mode High : Serial Control Mode                                                                            |  |  |

| 11         | RST               | 1                                                          | Reset Terminal                                                                                                                    |  |  |

|            |                   |                                                            | Low : Reset ON High : Reset OFF                                                                                                   |  |  |

| 12         | V <sub>SS</sub>   | -                                                          | Logic Power GND, V <sub>ss</sub> =0V                                                                                              |  |  |

| 13         | MCK               | I                                                          | Master Clock Input Terminal                                                                                                       |  |  |

|            |                   |                                                            | 256f <sub>s</sub> clock inputs this terminal.                                                                                     |  |  |

| 14         | BCK               |                                                            | Serial Audio Data Bit Clock Input Terminal<br>This clock must synchronize with MCK input signal.                                  |  |  |

|            |                   |                                                            | L/R Channel Clock Input Terminal                                                                                                  |  |  |

| 15         | LRCK              | I                                                          | This clock must synchronize with MCK input signal.                                                                                |  |  |

| 16         | V <sub>DDR</sub>  | _                                                          | Rch Power Supply, $V_{DDR}=V_{DD}$ to 5.0V                                                                                        |  |  |

| 17         |                   | 0                                                          | Rch Negative Output Terminal                                                                                                      |  |  |

| 18         |                   | -                                                          | Rch Power GND, V <sub>SSR</sub> =0V                                                                                               |  |  |

| 10         |                   | -                                                          | Rch Positive Output Terminal                                                                                                      |  |  |

|            |                   | -                                                          |                                                                                                                                   |  |  |

| 20         |                   | -                                                          | Rch Power Supply, $V_{DDR}=V_{DD}$ to 5.0V                                                                                        |  |  |

| 21         | DIN               |                                                            | Serial Audio Data Input Terminal                                                                                                  |  |  |

|            |                   |                                                            | MODE="Low" : Serial Audio Interface Format Selection Terminal 2<br>MODE="High" : Control Register Data Shift Clock Input Terminal |  |  |

| 22         | F2/SCK            | I                                                          | The data is fetched into the control register by rise edge of SCK                                                                 |  |  |

|            |                   |                                                            | signal.                                                                                                                           |  |  |

|            |                   |                                                            | MODE="Low" : Serial Audio Interface Format Selection Terminal 1                                                                   |  |  |

|            |                   | MODE="High" : Control Register Data Request Input Terminal |                                                                                                                                   |  |  |

| <u>a</u> t |                   |                                                            | MODE="Low" : Serial Audio Interface Format Selection Terminal 0                                                                   |  |  |

| 24         | F0/DATA           | I                                                          | MODE="High" : Control Register Data Input Terminal                                                                                |  |  |

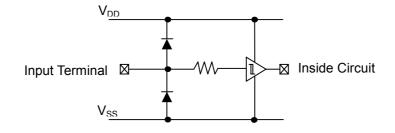

# ■ INPUT TERMINAL STRUCTURE

### FUNCTIONAL DESCRIPTION

(1) Signal Output

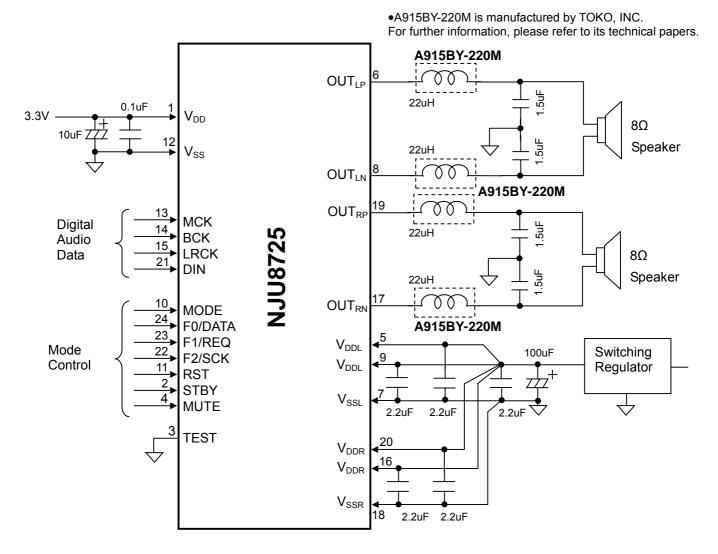

PWM signals of L channel and R output from  $OUT_{LP}/_{LN}$  and  $OUT_{RP}/_{RN}$  terminals respectively. These signals are converted to analog signal by external 2nd-order or over LC filter. The output driver power supplied from  $V_{DDL}$ ,  $V_{DDR}$ ,  $V_{SSL}$ , and  $V_{SSR}$  are required high response power supply against voltage fluctuation like as switching regulator because Output THD is effected by power supply stability.

(2) Master Clock

Master Clock is 256f<sub>S</sub> clock into MCK terminal for the internal circuit operation clock.

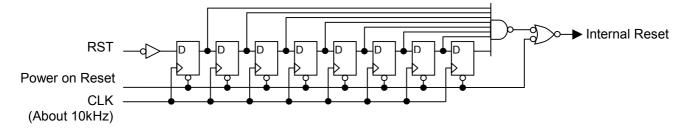

(3) Reset

"L" level input over than 3ms to the RST terminal is initialization signal to initialize the internal circuit. This initialization signal is synchronized with internal clock and executes logical OR with the internal power on reset signal. This Reset signal initializes the internal function setting registers also. During initialization, the output-drivers output GND level. The reset equivalent circuit is shown bellow.

Figure 1. Reset Equivalent Circuit

(4) 8f<sub>s</sub> Over Sampling Digital Filter

8f<sub>s</sub> Over Sampling Digital Filter interpolates Audio data and decreases aliasing noise. It realizes Attenuation and De-Emphasis function by serial function control.

#### (5) $32f_{S} 6^{th} \Delta \Sigma \& PWM$

$32f_S~6^{th}~\Delta\Sigma$  & PWM convert from Audio data of the  $8f_S$  Over Sampling Digital Filter to the  $32f_S$  one bit PWM data.

(6) Short Circuit Protection

Short Circuit Protection protects IC with output terminal of high-impedance condition when output terminal is shorted to GND or other output terminal.

The high-impedance condition is released automatically with master clock input, not released without master clock input.

# (7) System Control

### (7-1) Standby

Standby functions by "L" level input to the STBY terminal. In busy of Standby, conditions of digital audio format set, attenuation level, de-emphasis, and attenuator operation time are kept and output terminals are high-impedance.

## (7-2) Control Mode Set

A control mode as shown below is selected by the MODE terminal.

| MODE | Control Method | Function                           | Terminals      |

|------|----------------|------------------------------------|----------------|

| 0    | Parallel       | Digital Audio interface Format Set | F0, F1, F2     |

| 1    | Serial         | Control Register serial data input | DATA, REQ, SCK |

Parallel : Digital Audio Interface Format is set directly by using F0, F1, and F2 terminals.

Serial : **NJU8725** is controlled serial input data by 3-wire serial interface using DATA, REQ, and SCK terminals

By this setting, the function of F0/DATA, F1/REQ, and F2/SCK are changed. Refer to  $\lceil$  (8-5)F0,F1,F2  $\rfloor$  about function of F0, F1, and F2 terminals. Refer to  $\rceil$  (8)Control Register  $\rfloor$  about function of DATA, REQ, and SCK terminals.

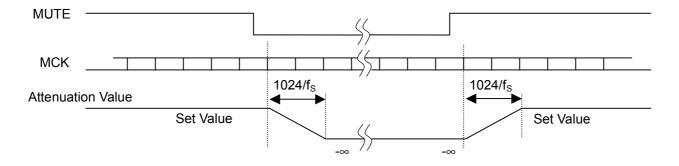

### (7-3) Mute

Mute functions by "L" signal into the MUTE terminal. In busy of mute, a current attenuation value becomes  $-\infty$  by internal digital attenuator. And MUTE is stopped by "H" signal into the MUTE terminal, the attenuation value returns from  $-\infty$  to previous value.

| MUTE | Attenuation Level |

|------|-------------------|

| 0    | -∞                |

| 1    | Set Value         |

Figure 2. Mute Timing

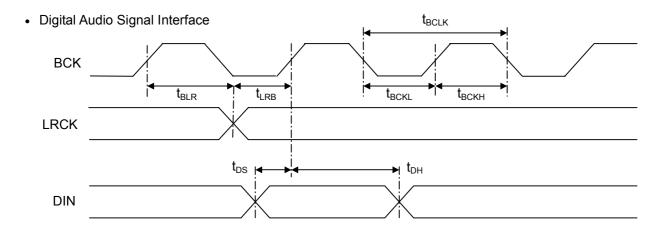

#### (8) Serial Audio Data Interface

#### (8-1) Input Data Format Selection

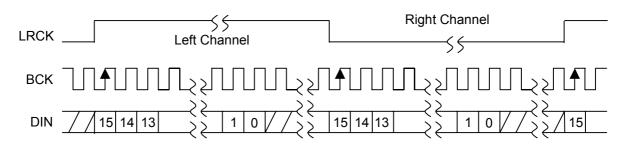

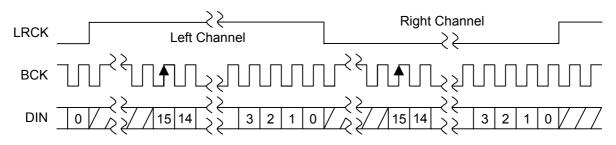

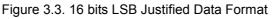

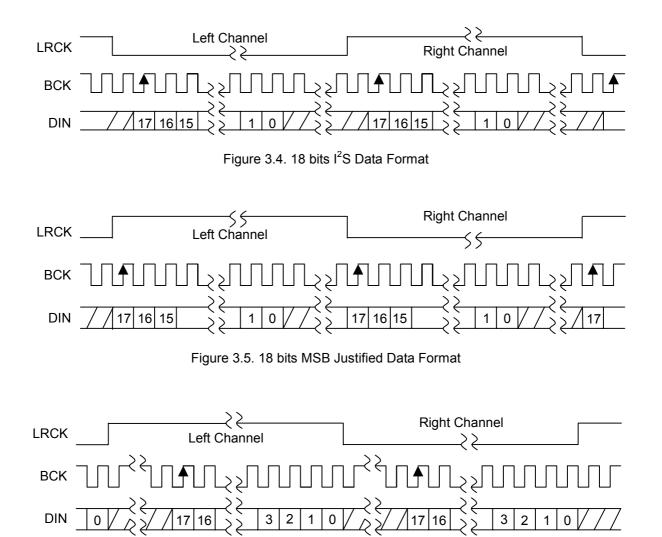

The digital audio interface format is selected out of I<sup>2</sup>S, MSB Justified or LSB Justified, and 16 bits or 18 bits data length.

#### (8-2) Input Timing

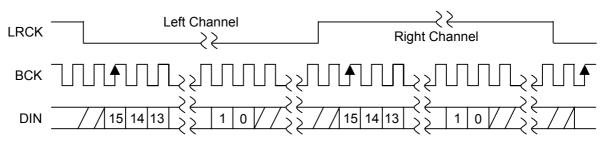

Digital audio signal data into DIN terminal is fetched into the internal shift register by BCK signal rising edge. The fetched data in the shift register are transferred by rising edge or falling edge of LRCK as shown below:

| Data Format      | Rising Edge        | Falling Edge       |

|------------------|--------------------|--------------------|

| l <sup>2</sup> S | Lch Input Register | Rch Input Register |

| MSB Justified    | Rch Input Register | Lch Input Register |

| LSB Justified    | Rch Input Register | Lch Input Register |

BCK and LRCK must be synchronized with MCK.

Figure 3.1. 16 bits I<sup>2</sup>S Data Format

Figure 3.2. 16 bits MSB Justified Data Format

Figure 3.6. 18 bits LSB Justified Data Format

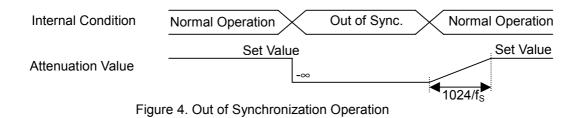

#### (8-3) Failure of Synchronization Operation

If the MCK clock fluctuates over than  $\pm 10$  clocks against the LRCK and failure of synchronization is detected the attenuation value is set to  $-\infty$ . When the LRCK synchronizes with MCK again, the attenuation value returns from  $-\infty$  to previous level.

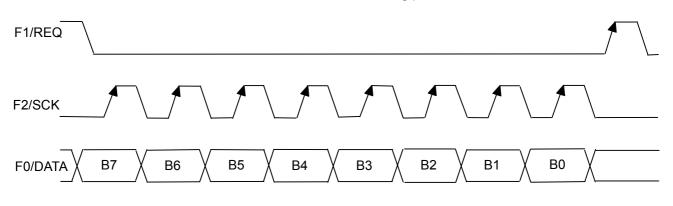

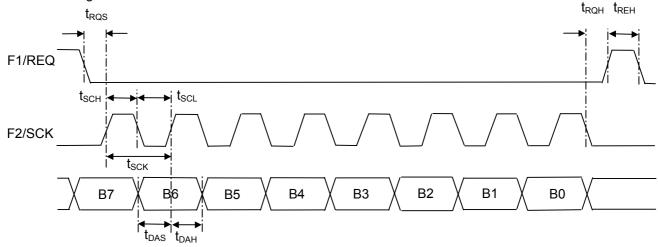

#### (9) Control Register

When Control Mode is set to Serial control by the Mode terminal, the control register sets various modes. The Control Data is fetched by the rising edge of F2/SCK and is set into the control register by the rising edge of F1/REQ. The latest 8 bits data are valid before the F1/REQ rising pulse.

Figure 5. Control Register Timing

#### (9-1) Serial Data Format

| _/ |       |       |       |       |       |       |       |

|----|-------|-------|-------|-------|-------|-------|-------|

| B7 | B6    | B5    | B4    | B3    | B2    | B1    | B0    |

| 0  | ATTN6 | ATTN5 | ATTN4 | ATTN3 | ATTN2 | ATTN1 | ATTN0 |

| 1  | 0     | 0     | 0     | 0     | 0     | DEMP1 | DEMP0 |

| 1  | 0     | 0     | 1     | F2    | F1    | F0    | MUTE  |

| 1  | 0     | 1     | 0     | 0     | 0     | 0     | RST   |

| 1  | 1     | 0     | 0     | 0     | 0     | 0     | TEST  |

| 1  | 1     | 0     | 1     | 0     | 0     | 0     | 0     |

| 1  | 1     | 1     | 0     | 0     | MUTT2 | MUTT1 | MUTT0 |

| 1  | 1     | 1     | 1     | 0     | 0     | 0     | TRST  |

Do not set other data excepting this table.

#### (9-2) ATTN6 to ATTN0

When B7 is "0", B0 to B6 set the attenuation data. When attenuation data is set, the attenuation value is changed to the target value in the period of transition time set by MUTT0 to MUTT2. The attenuation value (ATT) is fixed by following formula.

When ATT is 14h or less, the attenuator is set  $-\infty$  at reset. (When Control Mode is Parallel Control, ATT is fixed 0db.)

ATT=DATA -121[dB] DATA : attenuation point 7Fh=6 dB 7Eh=5dB 7Dh=4dB : 79h=0dB : 16h=-99dB 15h=-100dB 14h=- $\infty$ 13h=- $\infty$ : 00h=- $\infty$  (initial value)

### (9-3) DEMP0, DEMP1

DEMP0 and DEMP1 control De-Emphasis on/off and sampling frequency.

| DEMP1 | DEMP0 | De-Emphasis | Initial Value |

|-------|-------|-------------|---------------|

| 0     | 0     | OFF         | $\checkmark$  |

| 0     | 1     | 32kHz       |               |

| 1     | 0     | 44.1kHz     |               |

| 1     | 1     | 48kHz       |               |

(9-4) MUTE

Mute operation is controlled by the "MUTE" as same as the MUTE terminal control.

| MUTE | Mute Operation | Initial Value |  |

|------|----------------|---------------|--|

| 0    | OFF            | ✓             |  |

| 1    | ON             |               |  |

#### (9-5) F0, F1, F2

F0, F1, and F2 select Digital Audio Interface Format. As same as the F0/DATA, F1/REQ, and F2/SCK terminal control.

| F0 | F1 | F2 | Interface Format | Bit Length | Initial Value |

|----|----|----|------------------|------------|---------------|

| 0  | 0  | 0  | l <sup>2</sup> S | 16         | $\checkmark$  |

| 0  | 0  | 1  | MSB Justified    | 16         |               |

| 0  | 1  | 0  | LSB Justified    | 16         |               |

| 1  | 0  | 0  | l <sup>2</sup> S | 18         |               |

| 1  | 0  | 1  | MSB Justified    | 18         |               |

| 1  | 1  | 0  | LSB Justified    | 18         |               |

(9-6) RST

When the RST is "1", the control register and inner data (Digital filter, PWM modulator) are initialized.

| RST | Reset Operation | Initial Value |  |

|-----|-----------------|---------------|--|

| 0   | OFF             | ✓             |  |

| 1   | ON              |               |  |

(9-7) TRST

When the TRST is "1", only inner data (Digital filter, PWM modulator) is initialized.

| TRST | Data Bus Initialize | Initial Value |

|------|---------------------|---------------|

| 0    | OFF                 | ✓             |

| 1    | ON                  |               |

### (9-8) MUTT2 to MUTT0

MUTT2 to MUTT0 set the attenuator transition time. This transition time is one attenuation step change time.

| MUTT2 | MUTT1 | MUTT0 | Operation Time       | Initial Value |

|-------|-------|-------|----------------------|---------------|

| 0     | 0     | 0     | 1 / f <sub>s</sub>   | ✓             |

| 0     | 0     | 1     | 2 / f <sub>s</sub>   |               |

| 0     | 1     | 0     | 4 / f <sub>S</sub>   |               |

| 0     | 1     | 1     | 8 / f <sub>S</sub>   |               |

| 1     | 0     | 0     | 16 / f <sub>s</sub>  |               |

| 1     | 0     | 1     | 32 / f <sub>S</sub>  |               |

| 1     | 1     | 0     | 64 / f <sub>s</sub>  |               |

| 1     | 1     | 1     | 128 / f <sub>s</sub> |               |

### ■ ABSOLUTE MAXIMUM RATINGS

|                          |                  |                              | (Ta=25°C) |

|--------------------------|------------------|------------------------------|-----------|

| PARAMETER                | SYMBOL           | RATING                       | UNIT      |

|                          | V <sub>DD</sub>  | -0.3 to +4.0                 | V         |

| Supply Voltage           | V <sub>DDL</sub> | -0.5 to +5.5                 | V         |

|                          | V <sub>DDR</sub> | -0.5 to +5.5                 | V         |

| Input Voltage            | Vin              | -0.3 to V <sub>DD</sub> +0.3 | V         |

| Operating Temperature    | Topr             | -40 to +85                   | О°        |

| Storage Temperature      | Tstg             | -40 to +125                  | О°        |

| Power Dissipation SSOP24 | PD               | 600                          | mW        |

Note 1) All voltage values are specified as  $V_{SS} = V_{SSR} = V_{SSL} = 0V$ .

Note 2) If the LSI is used on condition beyond the absolute maximum rating, the LSI may be destroyed. Using LSI within electrical characteristics is strongly recommended for normal operation. Use beyond the electrical characteristics conditions will cause malfunction and poor reliability.

Note 3) Decoupling capacitors should be connected between  $V_{DD}$ - $V_{SS}$ ,  $V_{DDR}$ - $V_{SSR}$  and  $V_{DDL}$ - $V_{SSL}$  due to the stabilized operation.

### ELECTRICAL CHARACTERISTICS

(Ta=25°C,  $V_{DD}=V_{DDL}=V_{DDR}=3.3V$ ,  $f_{S}=44.1kHz$ , Input Signal=1kHz,

Input Signal Level at Full Scale Output, MCK=256f\_s, Load Impedance=8 $\Omega$ ,

Measuring Band=20Hz to 20kHz, 2<sup>nd</sup>-order 28kHz LC Filter (Q=2),

| unless othe | rwise noted) |

|-------------|--------------|

|-------------|--------------|

|                                                    |                 |                                         |                 |      | unicoo          | ounerwise | noted |

|----------------------------------------------------|-----------------|-----------------------------------------|-----------------|------|-----------------|-----------|-------|

| PARAMETER                                          | SYMBOL          | CONDITIONS                              | MIN.            | TYP. | MAX.            | UNIT      | Note  |

| V <sub>DDL</sub> , V <sub>DDR</sub> Supply Voltage |                 |                                         | V <sub>DD</sub> | -    | 5.25            | V         |       |

| V <sub>DD</sub> Supply Voltage                     |                 |                                         | 3.0             | 3.3  | 3.6             | V         |       |

| Output Power Efficiency                            | Eeff            | Vo= 0dB                                 | 80              | -    | -               | %         | 4     |

| Output THD                                         | THD             | Vo=-6dB                                 | -               | -    | 0.1             | %         |       |

| Output Power                                       | Po              | Vo= 0dB                                 | TBD             | 800  | -               | mW/ch     |       |

| S/N                                                | SN              | A weight                                | 85              | 90   | -               | dB        |       |

| Dynamic Range                                      | Drange          | A weight                                | 85              | 90   | -               | dB        |       |

| Channel Separation                                 | Echn            | EIAJ(1kHz)                              | 60              | -    | -               | dB        |       |

| Output Level Difference<br>Between Lch and Rch     | CHD             |                                         | -               | -    | 3               | dB        |       |

| Maximum Mute Attenuation                           | MAT             |                                         | 90              | -    | -               | dB        |       |

| Passband Response                                  | PR              | 20Hz to 20kHz                           | -               | -    | ±1              | dB        |       |

| Power Supply Current<br>At Standby                 | I <sub>ST</sub> | Stopping MCK,<br>BCK, LRCK, DIN         | -               | -    | 10              | μA        |       |

| Power Supply Current<br>At Operating               | I <sub>DD</sub> | No-load operating<br>No signal inputted | -               | 13   | 20              | mA        |       |

| Input Voltage                                      | V <sub>IH</sub> |                                         | $0.7V_{DD}$     | -    | V <sub>DD</sub> | V         |       |

| input voitage                                      | VIL             |                                         | 0               | -    | $0.3V_{DD}$     | V         |       |

| Input Leakage Current                              | I <sub>LK</sub> |                                         | -               | -    | ±1.0            | μA        |       |

Note 4)

Power Efficiency (%)

OUT<sub>L</sub> Output Power + OUT<sub>R</sub> Output Power (W)

$= \frac{1}{V_{DDL} \text{ Supply Power + } V_{DDR} \text{ Supply Power (W)}} \times 100$

New Japan Radio Co., Ltd.

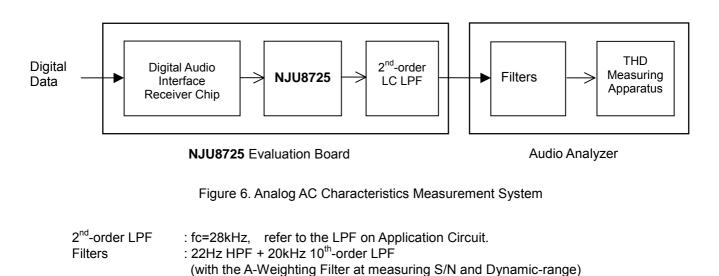

#### Note 5) Analog AC Characteristics Test System

Analog AC characteristics test system is shown in Figure 6. The analog AC characteristics of **NJU8725** is measured with 2<sup>nd</sup>-order LC LPF on the test board and Filters in the Audio Analyzer.

# **TIMING CHARACTERISTICS**

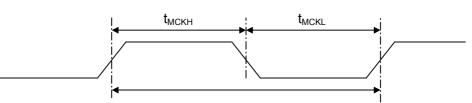

Master Clock Input

MCK

(Ta=25°C,  $V_{DD}=V_{DDL}=V_{DDR}=3.3V$ , unless otherwise noted)

| -                   |                   |                   | 00 000 | 5511 |        | ,    |

|---------------------|-------------------|-------------------|--------|------|--------|------|

| PARAMETER           | SYMBOL            | CONDITIONS        | MIN.   | TYP. | MAX.   | UNIT |

| MCK Frequency       | f <sub>мскі</sub> | 256f <sub>S</sub> | 7.28   | -    | 27.648 | MHz  |

| MCK Pulse Width (H) | t <sub>мскн</sub> |                   | 12     | -    | -      | ns   |

| MCK Pulse Width (L) | t <sub>MCKL</sub> |                   | 12     | -    | -      | ns   |

Note 6)  $t_{MCKI}$  shows the cycle of the MCK signal.

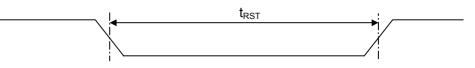

Reset Input

RST

(Ta=25°C, V\_{DD}=V\_{DDL}=V\_{DDR}=3.3V, unless otherwise noted)

| PARAMETER             | SYMBOL           | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|-----------------------|------------------|------------|------|------|------|------|

| Reset Low Level Width | t <sub>RST</sub> |            | 3    | -    | -    | ms   |

|                         |                   | (Ta=25°C   | C, V <sub>DD</sub> =V <sub>DDL</sub> = | ∶V <sub>DDR</sub> =3.3V, | unless other | wise noted) |

|-------------------------|-------------------|------------|----------------------------------------|--------------------------|--------------|-------------|

| PARAMETER               | SYMBOL            | CONDITIONS | MIN.                                   | TYP.                     | MAX.         | UNIT        |

| Audio DAC Sampling Rate | f <sub>S</sub>    |            | 28                                     | -                        | 100          | KHz         |

| DIN Setup Time          | t <sub>DS</sub>   |            | 20                                     | -                        | -            | ns          |

| DIN Hold Time           | t <sub>DH</sub>   |            | 20                                     | -                        | -            | ns          |

| BCK Period              | t <sub>BCLK</sub> |            | 1/(128f <sub>s</sub> )                 | -                        | -            | ns          |

| BCK Pulse Width (H)     | t <sub>вскн</sub> |            | 20                                     | -                        | -            | ns          |

| BCK Pulse Width (L)     | t <sub>BCKL</sub> |            | 20                                     | -                        | -            | ns          |

| LRCK Hold Time          | t <sub>BLR</sub>  |            | 20                                     | -                        | -            | ns          |

| LRCK Setup Time         | t <sub>LRB</sub>  |            | 20                                     | -                        | -            | ns          |

New Japan Radio Co., Ltd.

Control Register Interface

(Ta=25°C,  $V_{DD}=V_{DDL}=V_{DDR}=3.3V$ , unless otherwise noted)

| PARAMETER              | SYMBOL           | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|------------------------|------------------|------------|------|------|------|------|

| F2/SCK Period          | t <sub>scк</sub> |            | 2    | -    | -    | μs   |

| F2/SCK Pulse Width (H) | t <sub>SCH</sub> |            | 0.8  | -    | -    | μs   |

| F2/SCK Pulse Width (L) | t <sub>scL</sub> |            | 0.8  | -    | -    | μs   |

| F0/DATA Setup Time     | t <sub>DAS</sub> |            | 0.8  | -    | -    | μs   |

| F0/DATA Hold Time      | t <sub>DAH</sub> |            | 0.8  | -    | -    | μs   |

| F1/REQ Pulse Width (H) | t <sub>REH</sub> |            | 1.6  | -    | -    | μs   |

| F2/SCK Setup Time      | t <sub>RQS</sub> |            | 0.8  | -    | -    | μs   |

| F1/REQ Hold Time       | t <sub>RQH</sub> |            | 0.8  | -    | -    | μs   |

• Input Signal Rise and Fall Time

(Ta=25°C,  $V_{DD}=V_{DDL}=V_{DDR}=3.3V$ , unless otherwise noted)

| PARAMETER | SYMBOL          | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|-----------|-----------------|------------|------|------|------|------|

| Rise Time | t <sub>UP</sub> |            | -    | -    | 100  | ns   |

| Fall Time | t <sub>DN</sub> |            | -    | -    | 100  | ns   |

Note 7) All timings are based on 30% and 70% voltage level of  $V_{\text{DD}}.$

**APPLICATION CIRCUIT**

- Note 8) De-coupling capacitors must be connected between each power supply pin and GND pin.

- Note 9) The power supply for V<sub>DDL</sub> and V<sub>DDR</sub> require fast driving response performance such as a switching regulator for THD.

- Note 10) The above circuit shows only application example and does not guarantee the any electrical characteristics. Therefore, please consider and check the circuit carefully to fit your application.

<sup>[</sup>CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.